Simulacrum, từ simulacrum Latin, là một sự bắt chước, giả mạo hoặc hư cấu. Khái niệm này được liên kết với mô phỏng, đó là hành động mô phỏng .Một...

Giới thiệu ngôn ngữ VHDL

VHDL là gì?

VHDL là một ngôn từ diễn đạt phần cứng. Nó miêu tả hoạt động giải trí của một mạch điện tử hoặc mạng lưới hệ thống, từ đó mạch vật lý hoặc mạng lưới hệ thống hoàn toàn có thể được triển khai .

VHDL là viết tắt của cụm từ Very High Speed Intergrated Circuit Hardware Description Language – ngôn từ diễn đạt phần cứng cho những mạch tích hợp vận tốc rất cao. VHDL là ngôn từ diễn đạt phần cứng được tăng trưởng dùng cho chương trình VHSIC ( Very High Speed Intergrated Circuit ) của bộ quốc phòng Mỹ. Mục tiêu của việc tăng trưởng VHDL là có được một ngôn từ miêu tả phần cứng tiêu chuẩn và thống nhất được cho phép tăng trưởng thử nghiệm những mạng lưới hệ thống số nhanh hơn cũng như được cho phép thuận tiện đưa những mạng lưới hệ thống đó vào ứng dụng trong trong thực tiễn .

Hai ứng dụng chính của VHDL là trong nghành nghề dịch vụ PLD ( Programmable Logic Device – Thiết bị logic hoàn toàn có thể lập trình ( gồm có CPLD – Complex Programmable Logic Device và FPGA – Field Programmable Gate Array ) và trong nghành nghề dịch vụ ASIC ( Application Specific Integrated Circuit – Mạch tích hợp dành riêng cho ứng dụng ). Khi chương trình VHDL được viết, nó hoàn toàn có thể được sử dụng để thực thi mạch trong một thiết bị hoàn toàn có thể lập trình ( của Altera, Xilinx, Atmel, v.v. ) hoặc hoàn toàn có thể được gửi đến xưởng để sản xuất chip ASIC. Hiện nay, nhiều chip thương mại phức tạp ( ví dụ như vi tinh chỉnh và điều khiển ) được phong cách thiết kế theo cách tiếp cận như vậy .

Ưu điểm của VHDL

- Tính công cộng: VHDL được phát triển dưới sự bảo trợ của chính phủ Mỹ và hiện nay là một tiêu chuẩn của IEEE, VHDL không thuộc sở hữu của bất kỳ cá nhân hay tổ chức nào. Do đó VHDL được hỗ trợ của nhiều nhà sản xuất thiết bị cũng như nhiều nhà cung cấp công cụ thiết kế mô phỏng hệ thống. Ðây là một ưu điểm nổi bật của VHDL, giúp VHDL trở nên ngày càng phổ biến.

- Khả năng hỗ trợ nhiều công nghệ và phương pháp thiết kế: VHDL cho phép thiết kế bằng nhiều phương pháp như phương pháp thiết kế từ trên xuống, hay từ dưới lên dựa vào các thư viện có sẵn. Như vậy VHDL có thể phục vụ tốt cho nhiều mục đích thiết kế khác nhau, từ việc thiết kế các phần tử phổ biến đến việc thiết kế các IC ứng dụng đặc biệt (Application Specified IC).

- Ðộc lập với công nghệ: VHDL hoàn toàn độc lập với công nghệ chế tạo phần cứng. Một mô tả hệ thống dùng VHDL thiết kế ở mức cổng có thể được chuyển thành các bản tổng hợp mạch khác nhau tuỳ thuộc vào công nghệ chế tạo phần cứng nào được sử dụng (dùng CMOS, nMOS, hay GaAs). Ðây cũng là một ưu điểm quan trọng của VHDL nó cho phép người thiết kế không cần quan tâm đến công nghệ phần cứng khi thiết kế hệ thống, như thế khi có một công nghệ chế tạo phần cứng mới ra đời nó có thể được áp dụng ngay cho các hệ thống đã thiết kế.

- Khả năng mô tả mở rộng: VHDL cho phép mô tả hoạt động của phần cứng từ mức hệ thống số (hộp đen) cho đến mức cổng. VHDL có khả năng mô tả hoạt động của hệ thống trên nhiều mức nhưng chỉ sử dụng một cú pháp chặt chẽ thống nhất cho mọi mức. Như thế ta có thể mô phỏng một bản thiết kế bao gồm cả các hệ con được mô tả ở mức cao và các hệ con được mô tả chi tiết.

- Khả năng trao đổi kết quả: Vì VHDL là một tiêu chuẩn được chấp nhận, nên một mô hình VHDL có thể chạy trên mọi bộ mô phỏng đáp ứng được tiêu chuẩn VHDL và các kết quả mô tả hệ thống có thể được trao đổi giữa các nhà thiết kế sử dụng công cụ thiết kế khác nhau nhưng cùng tuân theo chuẩn VHDL. Hơn nữa, một nhóm thiết kế có thể trao đổi mô tả mức cao của các hệ thống con trong một hệ thống; trong khi các hệ con đó được thiết kế độc lập.

- Khả năng hỗ trợ thiết kế mức lớn và khả năng sử dụng lại các thiết kế: VHDL được phát triển như một ngôn ngữ lập trình bậc cao, vì vậy nó có thể sử dụng để thiết kế một hệ thống lớn với sự tham gia của một nhóm nhiều người. Bên trong ngôn ngữ VHDL có nhiều tính năng hỗ trợ việc quản lý, thử nghiệm và chia sẻ thiết kế. VHDL cũng cho phép dùng lại các phần đã có sẵn.

Quy trình thiết kế mạch bằng VHDL

Như đề cập ở trên, một trong số lớn các ứng dụng của VHDL là chế tạo các mạch hoặc hệ thống trong thiết bị có thể lập trình được (PLD hoặc FPGA) hoặc trong ASIC. Việc chế tao ra vi mạch sẽ được chia thành 3 giai đoạn như sau:

Bạn đang đọc: Giới thiệu ngôn ngữ VHDL

- Giai đoạn 1:

Chúng ta khởi đầu phong cách thiết kế bằng viết mã ( code ) VHDL. Các công ty sản xuất khác nhau như XILINX, Altera, v.v. phân phối những công cụ tăng trưởng ứng dụng của riêng họ như XILINX ISE, Altera Quartus, v.v. để sửa đổi, biên dịch và mô phỏng mã VHDL. Mã VHDL này sẽ được lưu vào file có đuôi là. vhd và có tên cùng với tên thực thể. Mã VHDL sẽ được diễn đạt ở cấp quy đổi thanh ghi ( RTL – Resister Transfer Level ) .

- Giai đoạn 2: Giai đoạn chế tạo

Bước đầu tiên trong quá trình chế tạo là biên dich. Quá trình biên dịch sẽ chuyển mã VHDL vào một netlist ở cấp cổng.

Bước thứ 2 của quá trình chế tạo là tối ưu. Quá trình tối ưu được thực hiện trên netlist ở cấp cổng để có tốc độ tốt hơn và chiếm ít không gian hơn. Trong giai đoạn này, thiết kế có thể được mô phỏng để kiểm tra phát hiện những lỗi xảy ra trong quá trình chế tạo.

Giai đoạn 3:

Là quy trình tiến độ ghép nối đóng gói ứng dụng. Ở quá trình này sẽ tạo ra sự sắp xếp vật lý cho chip PLD / FPGA hoặc tạo ra mặt nạ cho ASIC. Một lần nữa thiết bị ở đầu cuối hoàn toàn có thể được mô phỏng và xác định

Cấu trúc chương trình VHDL

Tất cả những chương trình VHDL gồm có tối thiểu ba thành phần cơ bản sau đây :

- Khai báo thư viện (LIBRARY): Chứa danh sách tất cả các thư viện sẽ được sử dụng trong thiết kế. Ví dụ: ieee, std, work, v.v.

- ENTITY (thực thể): Entity dùng để khai báo tên của thực thể, các port của thực thể và các thông tin liên quan đến

thực thể. - ARCHITECTURE ( kiến trúc ): Kiến trúc mô tả chức năng cơ bản của thực thể và chứa nhiều phát biểu mô tả hành vi của thực thể. Kiến trúc luôn luôn có liên quan đến thực thể và các mô tả hành vi của thực thể.

Cấu trúc của chương trình VHDL như sau :

LIBRARY library_name;

USE library_name.package_name.package_parts;

ENTITY entity_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

…);

END entity_name;

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

Khai báo thư viện

Thư viện chứa toàn bộ những đoạn code tiếp tục được sử dụng. Nó sẽ được cho phép tất cả chúng ta sử dụng lại nhiều lần. Ngoài ra, thư viện hoàn toàn có thể được san sẻ với những phong cách thiết kế khác .

Để khai báo thư viện (nghĩa là làm cho nó hiển thị trong thiết kế) cần phải có hai dòng lệnh, dòng thứ nhất bắt đầu bằng từ khóa LIBRARY tên thư viện (chú ý là VHDL không phân biệt chữ hoa chữ thường). Sau đó trên từng dòng kế tiếp sẽ khai báo các gói thư viện con mà thiết kế sẽ sử dụng, mỗi dòng phải kết thúc bằng dấu “;”.

|

LIBRARY library_name; |

Có ba thư viện thường được sử dụng trong toàn bộ những chương trình VHDL .

- ieee. std_logic_116

- standard

- work

Tuy nhiên, khi viết chương trình, tất cả chúng ta chỉ cần khai báo thư viện ieee vì hai thư viện còn lại là thư viện mặc định .

Mục đích của 3 gói / thư viện được kể ở trên là như sau : gói std_logic_1164 của thư viện ieee cho biết một hệ logic đa mức ; std là một thư viện tài nguyên ( kiểu dữ kiệu, i / o text .. ) cho thiên nhiên và môi trường phong cách thiết kế VHDL và thư viện work được sử dụng khi tất cả chúng ta lưu phong cách thiết kế ( file. vhd, những file được tạo bởi chương trình dịch và chương trình mô phỏng … ) .

Bây giờ để thêm những gói thư viện và một phần của nó, từ khóa USE được sử dụng với tên thư viện, những gói thư viện và những phần gói. Ví dụ trong thư viện IEEE, gói là std_logic_1164 và để thêm toàn bộ những phần của nó, tất cả chúng ta hoàn toàn có thể viết

LIBRARY ieee

USE ieee.std_logic_1164.all

ENTITY (thực thể)

Sau khai báo thư viện là Entity. Đây là thành phần chính của một cấu trúc chương trình VHDL .

Một khai báo Entity được dùng để miêu tả tiếp xúc I / O của mạch phong cách thiết kế. Phần thân của kiến trúc gồm có diễn đạt sự thực thi bên trong của thực thể đó, miêu tả link giữa những entity, giải quyết và xử lý và thành phần, những hàm, toán hạng …. Trong một phong cách thiết kế sẽ có rất nhiều entity link với nhau để triển khai tính năng mong ước .

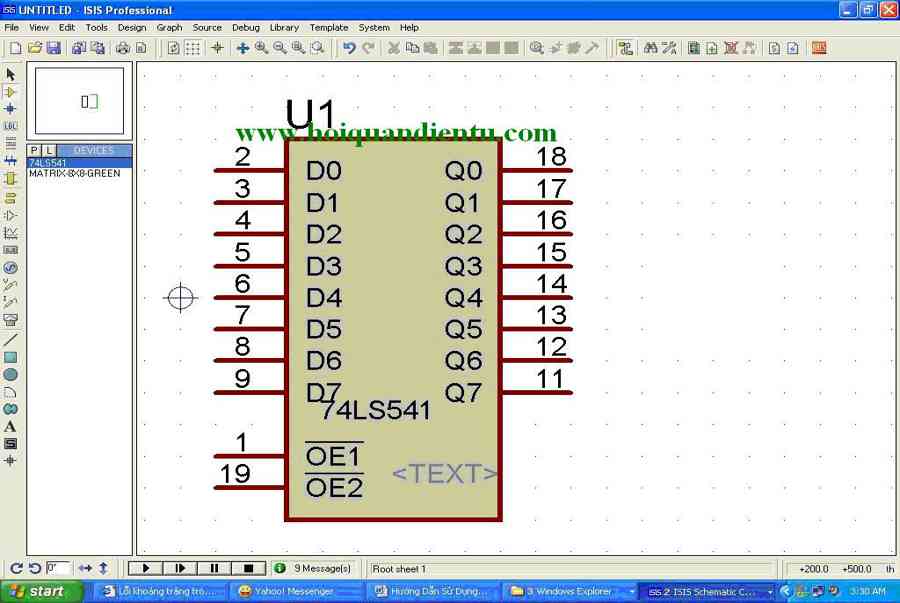

Khai báo Entity gồm có những list thông số kỹ thuật của toàn bộ những nguồn vào và đầu ra những PORT ( cổng ) của mạch. Cú pháp của nó được hiển thị dưới đây .

|

ENTITY entity_name IS |

Khai báo thực thể bắt đầu bằng từ khóa ENTITY sau đó là tên của thực thể và cuối cùng là từ khóa IS. Người viết chương trình phải đặt tên cho thực thể thường liên quan đến một mạch đang được thiết kế như ‘mux,’ ‘decoder,’ ‘adder,’ ‘counter’, v.v. (quy tắc chung cho bất kỳ chương trình VHDL nào là tên file chương trình phải giống với tên thực thể).

Bên trong thực thể, những chân đầu vào – đầu ra của mạch được khai báo bằng từ khóa PORT .

PORT ( nghĩa là những chân tiếp xúc ) được khai báo với port_name, signal_mode và signal_type .

port_name – là tên của chân đầu vào – đầu ra do người viết chương trình tự đặt .

signal_mode – có bốn loại chính sách IN, OUT, INOUT và BUFFER .

+ IN : Chỉ hoàn toàn có thể được đọc, nó chỉ được dùng cho những tín hiệu nguồn vào ( chỉ được phép nằm bên phải phép gán ) .

+ OUT : Chỉ được dùng để gán giá trị, nó chỉ được dùng cho những cổng đầu ra ( nó chỉ được nằm bên trái của phép gán ) .

+ INOUT : Có thể được dùng để đọc và gán giá trị. Nó hoàn toàn có thể có nhiều hơn một hướng điều khiển và tinh chỉnh ( hoàn toàn có thể nằm ở bên trái hoặc bên phải phép gán ) .

+ BUFFER : Có thể được dùng để đọc và gán giá trị ( hoàn toàn có thể nằm ở bên trái hoặc bên phải phép gán ). Inout là một cổng hai hướng, còn Buffer là một cổng không có hướng .

signal_type – chỉ ra kiểu tín hiệu của một cổng, hoàn toàn có thể là BIT, STD_LOGIC, INTEGER, …

entity_name ( tên của thực thể ) hoàn toàn có thể lấy một tên bất kể, ngoại trừ những tù khóa của VHDL.

Sau khi khai báo toàn bộ những chân tiếp xúc, khai báo thực thể kết thúc bằng từ khóa END theo sau là tên thực thể .

Ví dụ: Cổng NAND 2 ngõ vào, khai báo ENTITY như sau:

ENTITY nand_gate IS

PORT (a, b : IN BIT;

x : OUT BIT);

END nand_gate;

ARCHITECTURE (Kiến trúc)

ARCHITECTURE là một diễn đạt về phương pháp mạch hoạt động giải trí ( công dụng ). Một thực thể hoặc mạch hoàn toàn có thể được hoạt động giải trí theo nhiều kiểu khác nhau, ví dụ điển hình như hành vi, cấu trúc hoặc một sự tổng hợp 2 cách trên. Một kiến trúc gồm có những phần : Khai báo những những tín hiệu, hằng, khai báo những kiểu, những thành phần, tiếp theo là những phát biểu ( lệnh ) tuần tự hoặc đồng thời. Cú pháp cơ bản của architecture như sau :

|

ARCHITECTURE architecture_name OF entity_name IS |

Architecture phân phối thông tin cụ thể nội bộ của một thực thể có nghĩa là cách nguồn vào – đầu ra được liên kết với nhau. Nó miêu tả hành vi của mạch có nghĩa là cách mạch tạo ra đầu ra thiết yếu từ những nguồn vào nhất định .

Khai báo kiến trúc mở màn bằng từ khóa ARCHITECTURE theo sau là architecture_name và entity_name .

Từ khóa BEGIN cho biết phần khởi đầu của phần thân kiến trúc. Phần thân gồm có những câu lệnh tuần tự hoặc đồng thời miêu tả tính năng mạch .

Phần thân kiến trúc kết thúc bằng từ khóa END theo sau là architecture_name .

Ví dụ: Đây là kiến trúc của cổng NAND 2 đầu vào có .

ARCHITECTURE myarch OF nand_gate IS

BEGIN

x <= a NAND b;

END myarch;

Có ba kiểu quy mô khác nhau cho phần thân kiến trúc :

- Kiểu hoạt động của các luồng dữ liệu (Dataflow) – theo kiểu mô hình này, mạch được mô tả bằng cách sử dụng các câu lệnh đồng thời.

- Kiểu hành vi hoạt động (Behavioral) – trong kiểu mô hình này, mạch được mô tả bằng cách sử dụng các câu lệnh tuần tự.

- Kiểu cấu trúc (Structure) – theo kiểu mô hình này, mạch được mô tả bằng cách sử dụng các thành phần được kết nối với nhau.

Kiến trúc theo kiểu hoạt động của các luồng dữ liệu (Dataflow)

Một kiến trúc kiểu luồng tài liệu chỉ ra một mạng lưới hệ thống dưới dạng diễn đạt đồng thời của những luồng tinh chỉnh và điều khiển và di dời của tài liệu. Nó sử dụng theo mẫu thông tin hoặc mẫu hoạt động giải trí của luồng tài liệu đó, hoặc mẫu thời hạn của những tính năng logic tổng hợp. Chẳng hạn như những bộ cộng, bộ so sánh, bộ giải thuật, và những cổng logic .

Ví dụ:

architecture DATAFLOW of FULL_ADDER is

signal S : BIT ;

begin

S < = A xor B ;

SUM < = S xor CIN after 10 ns ;

COUT < = ( A and B ) or ( S and CIN ) after 5 ns ;

end DATAFLOW ;

Kiến trúc theo kiểu hành vi hoạt động (Behavioral)

Một kiến trúc kiểu hành vi hoạt động giải trí chỉ ra những hoạt động giải trí mà một mạng lưới hệ thống riêng không liên quan gì đến nhau nào đó phải thực thi trong một chương trình, nó giống như việc diễn đạt những quy trình hoạt động giải trí, nhưng không phân phối chi tiết cụ thể mà phong cách thiết kế được thực thi như thế nào. Thành phần đa phần của việc diễn đạt theo kiểu hành vi trong VHDL là process. Dưới đây là ví dụ chỉ ra kiểu diễn đạt theo kiểu hành vi của một bộ cộng với tên là FULL_ADDER .

architecture BEHAVIOUR of FULL_ADDER is

begin

process ( A, B, CIN )

begin

if ( A = ’ 0 ′ and B = ’ 0 ′ and CIN = ’ 0 ′ ) then

SUM < = ‘ 0 ’ ;

COUT < = ‘ 0 ’ ;

elsif

( A = ’ 0 ′ and B = ’ 0 ′ and CIN = ’ 1 ′ ) or

( A = ’ 0 ′ and B = ’ 1 ′ and CIN = ’ 0 ′ ) or

( A = ’ 1 ′ and B = ’ 0 ′ and CIN = ’ 0 ′ ) then

SUM < = ‘ 1 ’ ;

COUT < = ‘ 0 ’ ;

elsif

( A = ’ 0 ′ and B = ’ 1 ′ and CIN = ’ 1 ′ ) or

( A = ’ 1 ′ and B = ’ 0 ′ and CIN = ’ 1 ′ ) or

( A = ’ 1 ′ and B = ’ 1 ′ and CIN = ’ 0 ′ ) then

SUM < = ‘ 0 ’ ;

COUT < = ‘ 1 ’ ;

elsif ( A = ’ 1 ′ and B = ’ 1 ′ and CIN = ’ 1 ′ ) then

SUM < = ’ 1 ′ ;

COUT < = ’ 1 ′ ;

end if ;

end process ;

end BEHAVIOURAL ;

Kiến trúc theo kiểu cấu trúc (Structure)

Một kiến trúc kiểu cấu trúc chỉ ra sự thực thi cấu trúc theo dạng sử dụng những khai báo thành phần và những bộc lộ của thành phần đó. Ví dụ dưới đây chỉ ra sự miêu tả cấu trúc của một bộ cộng FULL_ADDER như trên đã trình làng .

Hai kiểu thành phần được sử dụng trong ví dụ này là HALF_ADDER và OR_GATE .

architecture STRUCTURE of FULL_ADDER is

component HALF_ADDER

port ( L1, L2 : in BIT ;

CARRY, SUM : out BIT ) ;

end component ;

component OR_GATE

port ( L1, L2 : in BIT ;

O : out BIT ) ;

end component ;

begin

HA1: HALF_ADDER port map (A,B,N1,N2);

HA2 : HALF_ADDER port map ( N2, CIN, N3, SUM ) ;

OR1 : OR_GATE port map ( N1, N3, COUT ) ;

end STRUCTURE ;

Source: https://vh2.com.vn

Category : Tin Học