Simulacrum, từ simulacrum Latin, là một sự bắt chước, giả mạo hoặc hư cấu. Khái niệm này được liên kết với mô phỏng, đó là hành động mô phỏng .Một...

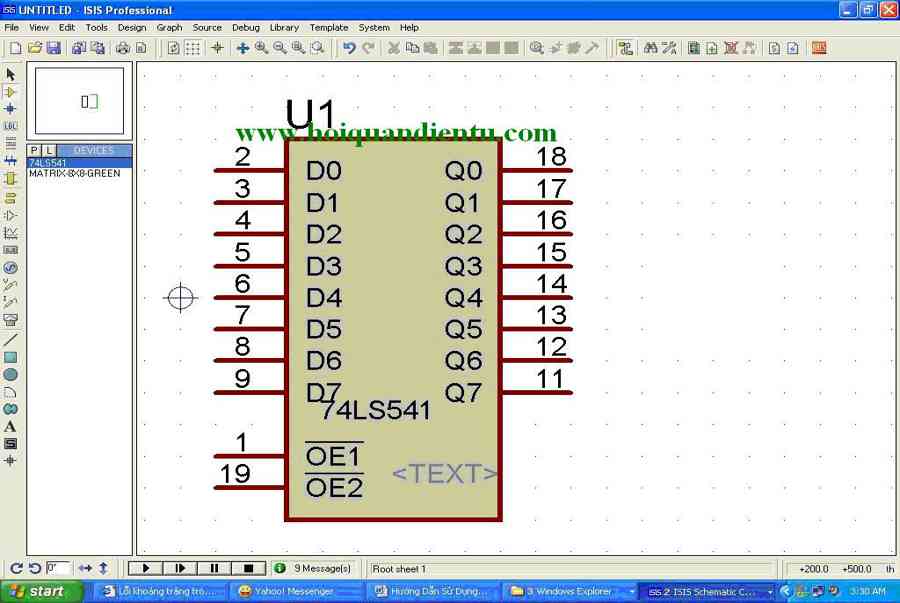

Đặc điểm, cấu trúc phần cứng của họ vi điều khiển AVR – Tài liệu text

Đặc điểm, cấu trúc phần cứng của họ vi điều khiển AVR

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (749.46 KB, 25 trang )

-1-1-

Đặc điểm, cấu trúc phần cứng của họ vi điều khiển AVR

4.1. Đặc điểm của họ vi điều khiển AVR

AVR là tên của một loạt các bộ vi điều khiển do công ty Atmel sản xuất, có

kiến trúc RISC (Reduced Instruction Set Computer) là một kiến trúc phổ biến trong

của các bộ xử lý hiện đại với những đặc tính sau:

1. Kiến trúc RISC với hầu hết các lệnh có chiều dài cố định, truy nhập bộ nhớ nạp,

lưu trữ và 32 thanh ghi đa năng.

2. Kiến trúc bộ nhớ kiểu đường ống cho phép làm tăng tốc độ xử lý lệnh.

3. Có chứa bộ phận ngoại ngay trên chip bao gồm các cổng I/O số, các bộ biến đổi

ADC, bộ nhớ EEFROM, bộ định thời UART, bộ định thời RTC, bộ điều chế độ

rộng xung PWM,.v.v.. Đặc điểm này được xem là nổi bật so với nhiều vi điều

khiển khác vì trong khi các bộ vi xử lý khác phải tự tạo ra bộ truyền nhận

UART hoặc giao diện SPI bằng phần mềm thì trên vi điều khiển AVR đã được

tích hợp sẵn:

Có 48 đường dẫn I/O lập trình được.

bộ truyền nhận UART lập trình được.

Một giao diện SPI đồng bộ.

bộ timer/Counter 8 bit

Một bộ timer/Counter 16 bit với chức năng so sánh và bắt mẫu.

Gồm bốn lối ra điều biến độ rộng xung PWM.

Một đồng hồ thời gian thực (RTC-Timer)

Một bộ biến đổi ADC 10 bit có đến 8 kênh lối vào.

Một bộ phát hiện trạng thái sụt điện áp nguồn nuôi.

Một bộ so sánh Analog

Một bộ định thời Watchdog

4. Hầu hết các lệnh chỉ trừ lệnh nhảy và nạp/lưu trữ đều được thực hiện trong một chu

kì xung nhịp.

-2-25. Hoạt động với tốc độ đồng hồ đến 20 MHz. So với các họ vi điều khiển khác thì vi

điều khiển họ ATMEL có tần số xung nhịp cho phép tương đối cao, cụ thể là từ 0

đến 20MHz tùy theo từng loại cụ thể. Xung nhịp do bộ dao động tạo ra cũng chính

là xung nhịp của hệ thống, không hề phải qua bộ chia tần như trong trường hợp các

vi điều khiển ra đời trước đó, nên kéo theo tốc độ xử lý lệnh cao.

6. Khả năng thực hiện lệnh trong một chu kì xung nhịp, AVR có khả năng đạt đến tốc

độ xử lý 20 MPIS (triệu lệnh trong một giây)

Hình 4.1 So sánh thời gian thực thi lệnh giữa các bộ vi xử lý

Các vi điều khiển SX cũng có tần số xung nhịp cao hơn ở các vi điều khiển

AVR nhưng lại có dòng tiêu thụ tương đối lớn, ngoài ra lại không có các bộ phận

ngoại vi trên chíp rất tiện dụng cho người dùng như vi điều khiển AVR. Chính các

bộ phận ngoại vi tích hợp đã góp phần làm tăng tốc độ xử lý lệnh tính chung cho cả

hệ thống.

7. Bộ nhớ chương trình và dữ liệu được tích hợp ngay trên chíp AVR có tới 3 công

nghệ bộ nhớ khác nhau:

Bộ nhớ EPROM xóa được kiểu Flash (luôn luôn lập trình mới được) dùng cho

mã chương trình mà người dùng có thể lập trình được.

-3-3Bộ nhớ EPROM hay PROM xóa được bằng điện, nhưng nội dung bộ nhớ vẫn

giữ nguyên sau khi tắt điện áp nguồn. Chương trình người dùng có thể được lập

trình trong thời gian thựckhi hệ thống đang hoạt động

Bộ nhớ RAM tĩnh (SRAM) dùng cho các biến, nội dung của bộ nhớ sẽ mất đi

khi tắt điện áp nguồn. Ngoài ra, vi điều khiển AVR có tới 32 thanh ghi làm việc đa

năng, tất cả đều được nối trực tiếp với khối ALU (đơn vị logic số học) và được trao

đổi trực tiếp trên vùng địa chỉ bộ nhớ, cụ thể là 32 ô đầu tiên của bộ nhớ (0x00 đến

0xFF) tương ứng với thanh ghi làm việc đa năng R0-R31.

8. Khả năng lập trình được trong hệ thống do cách thiết kế và công nghệ bộ nhớ được

sử dụng mà các vi điều khiển có thể được lập trình ngay khi đang còn cấp nguồn

trên bản mạch. Không cần phải nhấc vi điều khiển ra ngoài bản mạch như nhiều họ

vi điều khiển khác. Các cổng giao tiếp RS-232 và SPI cho phép thao tác dễ dàng

thực hiện trên hệ thống.

9. Có tốc độ xử lý lớn hơn 12 lần so với các vi điều khiển CISC thông thường.

10. Hỗ trợ cho việc lập trình bằng ngôn ngữ bậc cao, chẳng hạn như ngôn ngữ C.

11. Tất cả các vi điều khiển đang lưu hành trên thị trường đều được chế tạo bằng công

nghệ CMOS 0.6 μm.

12. Điện áp làm việc cho phép từ 2.7V đến 6V.

13. Một kiến trúc đơn giản và hợp lý sẽ giúp người dùng tìm hiểu dễ dàng trong thời

gian ngắn.

14. Tập lệnh AVR có tới 113 lệnh cho phép lập trình một cách dễ dàng và đơn giản

bằng hợp ngữ, nhưng cấu trúc của bộ xử lý Atmel còn cho phép lập trình bằng

ngôn ngữ C.

4.2. Cấu trúc phần cứng của họ vi điều khiển AVR

4.2.1. Tổng quan về kiến trúc

Các thanh ghi đa năng truy cập nhanh gồm 32 thanh ghi 8 bit được truy cập

trong một chu kì xung nhịp. Điều này có nghĩa là trong 1 chu kì xung nhịp ALU

-4-4thực hiện được một phép toán: hai toán hạng được xuất từ các thanh ghi đa năng,

phép toán được thực hiện và kết quả được lưu trở lại vào tập các thanh ghi. 6 trong

số 32 thanh ghi này có thể dùng làm con trỏ địa chỉ gián tiếp 16 bit để định địa chỉ

không gian dữ liệu và cho phép tính địa chỉ hiệu dụng. Một trong 3 con trỏ địa chỉ

cũng được dùng làm con trỏ địa chỉ cho chức năng tìm kiếm bảng hằng số. Các

thanh ghi có chức năng bổ xung này là các thanh ghi 16 bit X,Y,Z.

ALU: Hỗ trợ các chức năng số học và chức năng logic giữa các thanh ghi. Các

phép toán trong thanh ghi cũng được thực hiện trong ALU.

Hình 4.2 Kiến trúc của bộ xử lý AVR

Ngoài chế độ định địa chỉ gián tiếp thanh ghi, chế độ định địa chỉ bộ nhớ

thông thường cũng có thể được dùng trong tập các thanh ghi đa năng. Nguyên nhân

là các thanh ghi đa năng được gán 32 địa chỉ thấp nhất trong không gian dữ liệu từ

-5-5$00 đếm $1F nên chúng được truy cập những vị trí thông thường.

Không gian bộ nhớ vào ra chứa 64 bit địa chỉ cho các chức năng ngoại vi của

CPU như các thanh ghi điều khiển, bộ Timer/Counter, bộ ADC và chức năng I/O

khác. Bộ nhớ I/O có thể truy cập trực tiếp hoặc như các vị trí trong không gian dữ

liệu ngay sau các vị trí của tập các thanh ghi đa năng từ địa chỉ $20 đến $5F.

AVR sử dụng kiến trúc Harvard với bộ nhớ và bus riêng biệt cho chương trình

và dữ liệu. Bộ nhớ chương trình được thực thi với một đường ống hai tầng. Trong

khi một lệnh đang được thực thi thì lệnh tiếp theo được nhập vào bộ nhớ chương

trình. Giải pháp này cho phép vác lệnh được thực thi trong mọi chu kì xung nhịp.

Bộ nhớ chương trình là bộ nhớ Flash lập trình được.

Trong quá trình gọi ngắt và chương trình con, địa chỉ trở về của bộ đếm lệnh

hay bộ đếm chương trình PC được đưa vào ngăn xếp. Ngăn xếp được cấp phát

trong bộ lưu dữ liệu SRAM nên kích thước chỉ bị giới hạn bởi dung lượng và

không gian đã sử dụng của bộ nhớ SRAM. Tất cả chương trình của người dùng

phải khởi tạo con trỏ ngăn xếp SP (Stack Pointer) khi bắt đầu chương trình (trước

khi chương trình con và ngắt được thực thi). Con trỏ ngăn xếp 16 bit SP được truy

cập để đọc/ghi trong không gian vào/ra. Bộ nhớ SRAM có thể được truy cập dễ

dàng thông qua 5 chế độ định địa chỉ được cung cấp trong kiến trúc AVR.

Khối ngắt mềm dẻo có các thanh ghi điều khiển trong không gian vào ra và

một bit cho phép ngắt toàn cục trong thanh ghi trạng thái. Mỗi ngắt đều có một

vector ngắt riêng. Các ngắt có thứ tự ưu tiên tương ứng với thứ tự vector ngắt của

chúng, địa chỉ của vector ngắt càng thấp thì thứ tự ưu tiên càng cao.

4.2.2. Các thanh ghi đa dụng

Tất cả các bộ vi điều khiển AVR đều có 32 thanh ghi đa năng. Một số trong các

thanh ghi này còn có các chức năng bổ xung. Tất cả thanh ghi được đặt tên từ R0

đến R31, tệp thanh ghi được tách thành hai phần, mỗi phần có 16 thanh ghi đánh số

từ R0 đến R15 và R16 đến R31. Tất cả các lệnh thao tác trên các thanh ghi đều có

-6-6thể truy cập trực tiếp và truy cập trong chu trình đơn đến tất cả các thanh ghi,

nhưng có một ngoại lệ là các lệnh SBCI, SUBI, CPI, ANDI và ORI cũng như WI,

các lệnh này chỉ tác động đến các thanh ghi từ R16 đến R31.

Các thanh ghi R0 và R26 đến R31 có các chức năng bổ sung. Thanh ghi R0

được sử dụng trong các lệnh nạp bộ nhớ chương trình LPM (Load Program

Memory), trong khi các thanh ghi R26 đến R31 được sử dụng làm các thanh ghi

con trỏ như trong hình minh họa bên dưới. Các thanh ghi con trỏ này được sử dụng

trong nhiều lệnh gián tiếp trong thanh ghi.

Hình 4.3 Tập thanh ghi của vi điều khiển AVR

4.2.3. Cổng ra vào

Tất cả các vi điều khiển AVR đều có một lượng lớn các cổng vào ra nằm trong

khoảng 3 bit trên vi điều khiển loại 90S2313 đến 48 bit Mega103. Tất cả các cổng

vào/ra của vi điều khiển AVR đều chịu được dòng điện đến 20mA nên rất thích hợp

với việc điều khiển trực tiếp các led vì không cần đến các mạch đệm bổ sung.

Tất cả các cổng vào/ra đều có 3 địa chỉ vào/ra đi kèm với chúng, ba địa chỉ vào

ra đều cần được đặt cấu hình cho các bít riêng biệt thành lối vào hoặc thành lối ra,

-7-7địa chỉ khác được cần đến để xuất dữ liệu và địa chỉ thứ 3 dùng để đọc dữ liệu về

(lối vào).

Các cổng được đánh số DDRx, PORTx, PINx cho một cổng x cho trước.

Để đọc dữ liệu của phần lối vào của một cổng, ta sử dụng thanh ghi PINx.

Thanh ghi PINx được nối tiếp với chân của cổng. Chân của cổng có thể cấp tín

hiệu để duy trì trạng thái theo mức điện áp cao (pull up) bên trong bằng cách ghi

giá trị “1” vào bit cổng ở vị trí PORTx. Các điện trở pull up có giá trị 30kΩ đến

150kΩ. Giá trị tương úng của dòng điện là 160 μA đến 33μA.

Hình 4.4 Các port đọc và ghi

Ngược lại nếu một giá trị “0” được ghi vào bit cổng ở địa chỉ PORTx thì trạng

thái pull up và chân lối vào chuyển theo trạng thái trở kháng cao.

4.2.4. Bộ nhớ SRAM

Bộ nhớ SRAM có trong hầu hết các bộ vi xử lý của vi điều khiển AVR. Dung

lượng của bộ nhớ SRAM thay đổi từ 128 byte tới 4kbyte. Bộ nhớ SRAM được truy

nhập bằng cách sử dụng nhiều lệnh truy nhập dữ liệu hoặc trực tiếp hoặc gián tiếp.

-8-8Bộ nhớ SRAM cũng được sử dụng cho ngăn xếp, thời gian truy nhập vào bộ nhớ

SRAM bằng 2 chu kì đồng hồ.

Giao tiếp với bộ nhớ SRAM ngoài.

Trên các bộ vi điều khiển AVR cỡ lớn đều có khả năng kết nối với bộ nhớ

SRAM ở bên ngoài. Để cho phép truy nhập bộ nhớ SRAM ngoài trên PortA và

PortC của các bộ điều khiển cũng như tín hiệu ALE dùng cho việc phân kênh địa

chỉ/dữ liệu, bit SRE (bit 7) trong thanh ghi MCUCR được đặt lên “1”. Thời gian

truy nhập mặc định đối với quá trình nhập lên SRAM ngoài là bằng 3 chu kì đồng

hồ. Thời gian này có thể làm tăng lên 4 chu kì đồng hồ bằng cách thiết lập bit SRW

(bit6) trong thanh ghi MCUCR. Hình sau minh họa chu trình truy nhập mở rộng

với một trạng thái chờ bổ sung thêm.

Hình 4.5 Kết nối SRAM ngoài với bộ vi điều khiển

4.2.5. Cấu trúc ngắt

Ngắt là một cơ cấu điều khiển dòng lệnh, cơ cấu này được thiết kế trên hầu hết

các bộ vi điều khiển. Trong quá trình giao tiếp của hệ thống bộ vi xử lý với thế giới

bên ngoài, nhiều sự việc xảy ra theo cách không đồng bộ, điều này gây khó khăn

cho bộ xử lý khi mà phải kiểm tra tất cả các thiết bị để giám sát sự di chuyển của

dữ liệu. Ngược lại, sẽ trở nên tốt hơn nếu các thiết bị này có thể loan báo sự đến

-9-9nơi của dữ liệu. Đây là cả những gì mà cơ cấu ngắt phải thực hiện. Thiết bị ngoại vi

sẽ ngắt việc thực thi chương trình chính và bộ xử lý tạm ngừng việc thực thi

chương trình bình thường để kiểm tra nguồn ngắt và thực hiện những thao tác đáp

ứng cần thiết. Sau khi đã hoàn thành những thao tác cần thiết, việc thực thi chương

trình đã bị ngắt sẽ tiếp tục. Chương trình ngắt chỉ đơn giản giống hệt như một

chương trình con chỉ ngoại trừ một đặc điểm là việc thực thi của đoạn chương trình

ngắt này không bị bộ xử lý chặn trước là sẽ xuất hiện vào thời điểm cụ thể nào.

Bộ vi điều khiện AVR có rất nhiều cấu trúc ngắt. Khả năng ngắt đã được chu

cấp cho hầu hết các thiết bị ngoại vi sao cho chương trình chính không cần phải

thường xuyên kiểm tra các thiết bị này.

1. Thiết bị ngoại vi ngắt bộ xử lý

2. Việc thực thi lệnh hiện tại được hoàn thành.

3. Địa chỉ của lệnh tiếp theo được lưu trữ trên ngăn xếp (thuộc phần cứng hoặc phần

mềm)

4. Địa chỉ ISR (đoạn chương trình ngắt) được nạp vào bộ đếm chương trình.

5. Bộ xử lý ISR.

6. Việc hoàn thành các thao tác thực thi ISR được chỉ báo bằng lệnh RETI.

7. Bộ xử lý nạp bộ đếm chương trình với giá trị được lưu trữ trên ngăn xếp và việc

thực thi chương trình bình thường lại được tiếp tục.

4.2.6. Bộ so sánh analog

Bộ so sánh analog so sánh các giá trị điện áp lối vào, cụ thể là ở lối vào AINO

(AC+) và AIN1 (AC-) với nhau. Nếu như điện áp ở lối vào AIN0 lớn hơn AIN1 thì

lối ra của bộ so sánh analog ACO (Analog Computer Output) được đặt lên mức 1.

Lối ra này có thể cho bộ Timer/Counter 1 để trigger xóa ngắt bộ so sánh analog.

– 10 – 10 –

Hình 4.6 Sơ đồ khối của bộ so sánh Analog

Bộ so sánh analog được điều khiển thông qua thanh ghi điều khiển và trạng

thái so sánh analog, thường viết tắt là ACSR, tại địa chỉ $08 trong vùng địa chỉ I/O

hoặc địa chỉ nhớ $28 trong vùng địa chỉ nhớ dữ liệu.

Bảng 4.1 Sắp xếp các chân của bộ so sánh Analog

4.2.7. Bộ biến đổi A/D bên trong

Các vi điều khiển AVR loại AT90S4434/8535 và Atmega 103/603 có một bộ

biến đổi ADC với độ phân giải là 10 bit.

Ngoài bộ ADC còn có bộ dồn kênh lối vào, mỗi lối có thể được dẫn riêng lẻ tới bộ

hiển thị ADC.

– 11 – 11 –

Hình 4.7 Sơ đồ khối bộ biến đổi ADC

Bảng 4.2 Các thanh ghi điều khiển bộ biến đổi ADC

Thanh ghi điều khiển bộ dồn kênh ADC

$07 ($27)

ADMUX

– 12 – 12 Thanh ghi trạng thái điều khiển ADC

ADCSR

$06 ($26)

Thanh ghi dữ liệu ADC (HIGH)

ADCH

$05 ($25)

Thanh ghi dữ liệu ADC (LOW)

ADCL

$04 ($24)

Bộ biến đổi ADC được biến đổi qua 4 thanh ghi ADMUX, ADCSR,ADCH và

ADCR trong vùng địa chỉ vào ra. Bằng thanh ghi 3DMUX, một trong 8 kênh được

lựa chọn để biến đổi tín hiệu số. Bộ biến đổi có thể hoạt động trong hai chế độ:

–

Quá trình biến đổi được người dùng khởi động

–

Quá trình biến đổi diễn ra liên tục

Bảng 4.3 Sự sắp xếp các chân lối vào của bộ biếm đổi ADC

Tín hiệu

AT90S8535/4434

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC6

ADC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

Việc kết thúc quá trình biến đổi nghĩa là thời điểm mà một tín hiệu analog đã

được số hóa và sẵn sàng chờ xử lý tiếp tục, sẽ được báo hiệu qua một cờ trong

thanh ghi trạng thái ADC (ADCSR). Trong thanh ghi ADCSR này người dùng có

thể lựa chọn một trong hai chế độ. Kết quả của quá trình biến đổi A/D được đặt ở

các thanh ghi ADCH (bit 8 và 9) và ADCL (bit 0 đến 7).

– 13 – 13 4.2.8. Bộ định thời watchdog bên trong

Bộ định thời Watchdog là bộ định thời điều khiển được và được sử dụng làm

thiết bị đánh thức trong trường hợp phần mềm bị rơi vào một hoặc một số vòng lặp

vô tận hoặc trong trường hợp việc thực thi chương trình bị mắc lỗi. Bộ định thời

watchdog có một lối ra, có khả năng đặt lại bộ điều khiển. Hình bên dưới.

Mạch định thời watchdog timer được giữ nhịp từ một bộ dao động RC riêng

biệt trên chip. Bằng cách điều khiển mạch chia tần số timer, khoảng thời gian reset

mạch Watchdog có thể điều chỉnh như hình minh họa trong bảng sau các khoảng

reset,mạch Watchdog cũng phụ thuộc vào điện áp nguồn nuôi.

Hình 4.8 Sơ đồ khối của bộ định thời Watchdog

Chế độ hoạt động tiết kiệm năng lượng:

Bộ vi xử lý AVR có nhiều khả năng làm giảm năng lượng tiêu thụ để chuyển

sang trạng thái ngủ (sleep mode), bit SE trong MCUCR (mở thanh ghi điều khiển

bộ xử lý) phải được đặt lên “1”, một lệnh sleep cần phải được thực thi. Nếu một

ngắt đã được cho phép xuất hiện trong khi MCU đang ở trạng thái ngủ, thì MCU sẽ

Xem thêm: Tin học 12 Bài 12: Các loại kiến trúc của hệ cơ sở dữ liệu | Hay nhất Giải bài tập Tin học 12

thức dậy thực thi đoạn chương trình (routine) ngắt, và lại tiếp tục thực thi từ lệnh

kế tiếp theo lệnh sleep. Nội dung của tập thanh ghi, SRAM, và bộ nhớ I/O vẫn

được giữ nguyên. Nếu một tín hiệu reset xuất hiện trong trạng thái ngủ thì MCU sẽ

thức dậy và thực thi từ vector reset.

– 14 – 14 Khi SM bị xóa về không thì lệnh sleep bắt buộc MCU chuyển sang chế độ

nghỉ, làm ngưng hoạt động của CPU nhưng cho phép bộ Timer/Counter Watchdog

và ngắt hệ thống tiếp tục hoạt động. Đặc tính này cho phép MCU đánh thức và ngắt

được trigger từ bên ngoài cũng như ngắt bên trong giống như ngắt tràn bộ định thời

và đặt lại Watchdog. Nếu như sự đánh thức từ ngắt bộ so sánh analog không được

yêu cầu, thì bộ so sánh analog có thể bị ngắt nguồn nuôi bằng cách đặt bit ACD

vào thanh ghi điều khiển và trạng thái analog ACSR. Biện pháp này làm giảm dòng

tiêu thụ trong chế độ nghỉ.

Khi MCU bị đánh thức khỏi chế độ nghỉ, đơn vị CPU khởi động chương trình

chấp hành ngay lập tức.

Khi bit SM được đặt lên “1”, lệnh sleep bắt buộc MCU chuyển sang chế độ tiết

kiệm năng lượng hay giảm dòng tiêu thụ. Trong chế độ này bộ dao động ngoài bị

ngưng hoạt động, trong khi các ngắt ngoài và Watchdog (nếu đang ở trạng thái cho

phép) hoạt động. Chỉ thao tác đặt lại (reset) bên ngoài.

Thao tác đặt lại Watchdog (nếu đang ở trạng thái cho phép hoạt động) hoặc

ngắt theo mức ngoài lên INT0 hoặc INT1 mới có thể đánh thức MCU. Chú ý rằng

một khi ngắt trigger theo nức được sử dụng cho việc đánh thức khỏi trạng thái tiết

kiệm năng lượng thì mức thấp hơn cần năng lượng giữ trong khoảng thời gian dài

hơn thời gian làm trễ dài nhất (Time out) đối với thao tác reset TOUT. Nếu không

thì thiết bị sẽ không thức dậy.

4.3. Giới thiệu họ vi điều khiển Atmega 16

4.3.1. Đặc điểm

Atmega16 là bộ vi điều khiển RISC 8 bit tiêu thụ ít năng lượng dựa trên kiến

trúc RISC AVR. Bằng việc thực hiện các lệnh mạnh trong một chu kì xung nhịp,

Atmega16 đạt đên tốc độ xử lý lệnh lên đến 1 triệu lệnh/giây ở tần số 1MHz. Vi

điều khiển này còn cho phép người thiết kế hệ thống tối ưu hóa mức độ tiêu thụ

năng lượng mà vẫn đảm bảo tốc độ xử lý.

– 15 – 15 Phần cốt lỏi của AVR kết hợp tập lệnh phong phú về số lượng với 32 thanh ghi

làm việc đa năng. Toàn bộ 32 thanh ghi đều được nối với ALU cho truy cập hai

thanh ghi độc lập bằng một lệnh đơn trong một chu kì xung nhịp. Kiến trúc đạt tốc

độ xủ lý nhanh gấp 10 lần so với vi điều khiển CISC (Complex Instruction Set

Computer ) thông thường.

Atmega16 với kiến trúc RISC có chỉ tiêu chất lượng cao và tiêu thụ năng lượng ít:

131 lệnh hầu hết được thực hiện trong một chu kỳ xung nhịp.

32×8 thanh ghi làm việc đa năng.

Tốc độ xử lý lệnh lên đến 16 triệu lệnh/giây ở tần số 16MHz.

Bộ nhớ dữ liệu và bộ nhớ chương trình không tự mất dữ liệu:

16K byte bộ nhớ Flash lập trình được ngay trên hệ thống, có thể ghi xoá 10000 lần.

512 byte bộ nhớ EEFROM lập trình được ngay trên hệ thống, có thể ghi xóa

100000 lần.

1K byte bộ nhớ SRAM.

Khóa bảo mật phần mềm lập trình được.

Giao diện nối tiếp SPI để lập trình ngay trên hệ thống.

Các tính năng ngoại vi:

Hai bộ đếm/ bộ định thời 8 bit với chế độ so sánh và chia tần số tách biệt.

Một bộ định thời 16 bit với chế độ so sánh, chia tần số tách biệt và chế độ bắt mẫu

(Capture Mode).

Bộ đếm thời gian thực (RTC) với bộ dao động tách biệt.

Bốn kênh PWM điều chế độ rộng xung.

Bộ biến đổi ADC bên trong 8 kênh 10 bit.

Bộ USART nối tiếp lập trình được.

Bộ định thời Watchdog lập trình được với bộ dao động trên chip.

Bộ so sánh Analog ngay trên chip.

Các tính năng vi điều khiển đặc biệt:

Có mạch power – on reset và có thể reset bằng phần mềm.

– 16 – 16 Các nguồn ngắt ngoài và trong.

Có 6 chế độ ngủ: nghỉ (Idle). Tiết kiệm năng lượng (power save) và power down,

ADC Noise Reduction, Standby and Extended Standby.

Tần số làm việc có thể thay đổi được bằng phần mềm.

Vào ra và các cách đóng vỏ

32 đường vào ra lập trình được.

44 chân dán kiểu vỏ vuông (TQFP) Điện thế làm việc:

VCC = 2,7V đến 5,5V đối với Atmega16L.

VCC = 4,5V đến 5,5V đối với Atmega16.

Vùng tốc độ làm việc:

0 đến 8 MHz đối với Atmega16L.

0 đến 16 MHz đối với Atmega16.

4.3.2. Sơ đồ chân Atmega16

Hình 4.9 Sơ đồ chân Atmega16

– 17 – 17 –

4.3.3. Sơ đồ khối của Atmega16

– 18 – 18 Hình 4.10 Sơ đồ khối vi điều khiển AVR Atmega16

4.3.4. Mô tả chức năng các chân Atmega16

Vcc : điện áp nguồn nuôi

GND : nối đất

PORT A (PA0 … PA7) : có nhiều chức năng:

–

Là ngõ vào tín hiệu để chuyển đổi A/D

–

Là cổng vào ra 8 bit nếu như biến đổi A/D không sử dụng, các chân của

Port A có các điện trở nối lên nguồn dương. Port A có thể cung cấp nguồn

điện 20mA và điều khiển trực tiếp led hiển thị.

–

Khi các chân Port A là các lối vào được đặt xuống mức thấp ở bên ngoài chúng sẽ

là nguồn dòng nếu như các điện trở nối lên nguồn dương được kích hoạt. Các chân

này sẽ ở trạng thái tổng trở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khi

không có tín hiệu giữ nhịp.

PORT B (PB0 … PB7)

–

Là cổng vào ra 8 bit, có điện trở kéo lên ở bên trong, có thể cung cấp dòng điện

20mA. Khi port B là port nhập vào (in put) và các ngõ ra ở mức thấp (low) thì port

B đóng vai trò là nguồn dòng nếu các điện trở kéo lên được kích hoạt. Port B sẽ ở

trạng thái tổng trở cao khi vi điều khiển bị reset hoặc khi không có dao động.

PORT C (PC0 … PC7)

–

Là cổng vào ra theo hai hướng 8 bit. Các chân của Port C có các điện trở nối lên

nguồn dương. Ngõ ra port C có thể cho dòng 20mA đi qua và điều khiển trực tiếp

led hiển thị.

–

Khi các chân port C là các lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽ

là nguồn dòng nếu các điện trở nối lên nguồn dương được kích hoạt. các chân này

sẽ ở trạng thái tổng trở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khi

không có tín hiệu giữ nhịp.

PORT D (PD0 … PD7)

– 19 – 19 –

Là cổng vào ra theo hai hướng 8 bit. Các chân của Port D có các điện trở nối lên

nguồn dương. Ngõ ra port D có thể cho dòng 20mA đi qua và điều khiển trực tiếp

led hiển thị. Khi các chân port D là các lối vào được đặt xuống mức thấp từ bên

ngoài, chúng sẽ là nguồn dòng nếu các điện

trở nối lên nguồn dương được kích hoạt. các chân này sẽ ở trạng thái tổng

trở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khi không có tín

hiệu giữ nhịp.

–

Cung cấp các tính năng tương ứng với các chức năng đặc biệt.

Reset: là lối vào đặt lại. Bộ vi điều khiển sẽ được đặt lại khi chân này ở mức thấp

trong hơn 50ns ngay cả khi có tín hiệu giữ nhịp. Các xung ngắn hơn không tạo ra

tín hiệu đặt lại.

XTAL1: Lối vào mạch khuếch đại đảo và lối vào mạch tạo xung nhịp bên trong.

XTAL2: Lối vào bộ khuếch đại ảo.

ICP: Chân vào có chức năng bắt tín hiệu cho Timer/Cuonter 1

ALE: Là chân tín hiệu cho phép chốt địa chỉ (adress latch enable) được dùng khi

truy nhập bộ nhớ ngoài. Xung ALE được dùng để chốt bit địa chỉ trong chu kì truy

cập bộ nhó thứ nhất. Sau đó các chân AD0 … AD7 được dùng làm các đường dữ

liệu trong chu kì truy nhập bộ nhớ thứ hai (AT90S8515).

Bộ tạo dao động thạch anh: XTAL1 và XTAL2 lần lượt là lối vào và lối ra của một

bộ khuếch đại đảo, bộ khuếch đại này được bố trí để làm bộ tạo dao động trên chip

như hình 4.3. Một bộ cộng hưởng tinh thể thạch anh hoặc một bộ cộng hưởng gốm

có thể sử dụng. Để điều khiển vi điều khiển bằng nguồn xung nhịp bên ngoài thì

chân XTAL2 để không và nối XTAL một với tín hiệu dao động bên ngoài.

4.4. Giới thiệu vi điều khiển Atmega8

4.4.1. Đặc điểm

Vi điều khiển Atmega8 của hãng ATMEL là một loại vi điều khiển AVR mới

với kiến trúc rất phức tạp.

– 20 – 20 Atmega 8 là bộ vi điều khiển RISC 8 bit tiêu thụ năng lượng nhưng đạt hiệu

suất rất cao, dựa trên kiến trúc RISC AVR. Bằng việc thực hiện các lệnh trong một

chu kỳ xung nhịp, Atmega8 đạt được tốc độ xử lý dữ liệu lên đến 1 triệu lệnh/giây

ở tần số 1MHz. Atmega8 còn cho phép người thiết kế hệ thống tối ưu hoá mức độ

tiêu thụ năng lượng mà vẫn đảm bảo tốc độ xử lý.

Atmega 8 đã tích hợp đầy đủ các tính năng như bộ chuyển đổi ADC 10bit, bộ

so sánh, bộ truyền nhận nối tiếp, bộ định thời, bộ đếm thời gian thực, bộ điều chế

độ rộng xung…Do đó ta phải nghiên cứu và khai thác triệt để các tính năng này để

ứng dụng hiệu quả vào những mạch trong thực tế.

Atmega8 sử dụng kiến trúc RISC (Reduced Instruction Set Computer) AVR.

Atmega8 với kiến trúc RISC có chỉ tiêu chất lượng cao và tiêu thụ năng lượng ít:

–

130 lệnh hầu hết được thực hiện trong một chu kỳ xung nhịp.

–

32 thanh ghi làm việc đa năng.

–

Tốc độ xử lý lệnh lên đến 16 triệu lệnh/giây ở tần số 16MHz.

Bộ nhớ dữ liệu và bộ nhớ chương trình không tự mất dữ liệu:

–

8K byte bộ nhớ Flash lập trình được ngay trên hệ thống, có thể nạp xoá 10000 lần.

–

512 byte bộ nhớ EEFROM lập trình được ngay trên hệ thống, có thể ghi xóa

100000 lần.

–

1K byte bộ nhớ SRAM.

–

Có thể giao tiếp với 8K byte bộ nhớ ngoài.

–

Khóa bảo mật phần mềm lập trình được.

–

Giao diện nối tiếp SPI để lập trình ngay trên hệ thống.

Các tính năng ngoại vi:

–

Hai bộ đếm/ bộ định thời 8 bit với chế độ so sánh và chia tần số tách biệt.

–

Một bộ định thời 16 bit với chế độ so sánh, chia tần số tách biệt và chế độ bắt mẫu

(Capture Mode).

–

Bộ đếm thời gian thực (RTC) với bộ dao động tách biệt.

–

Bộ điều chế độ rộng xung PWM 8 bit.

– 21 – 21 –

Bộ biến đổi ADC bên trong 8 kênh 10 bit.

–

2 bộ USART nối tiếp lập trình được.

Bộ định thời Watchdog lập trình được với bộ dao động trên chip.

–

Một bộ so sánh Analog.

Các tính năng vi điều khiển đặc biệt:

–

Có mạch power – on reset và có thể reset bằng phần mềm.

–

Các nguồn ngắt ngoài và trong.

–

Có 5chế độ ngủ: nghỉ (Idle). Tiết kiệm năng lượng (power save) và power down,

ADC Noise Reduction, Standby.

–

Tần số làm việc có thể thay đổi được bằng phần mềm.

Vào ra và các cách đóng vỏ

–

23 đường vào ra lập trình được.

–

32 chân dán kiểu vỏ vuông (TQFP) Điện thế làm việc:

–

VCC = 2,7V đến 5,5V đối với Atmega8L.

–

VCC = 4,5V đến 5,5V đối với Atmega8.

Vùng tốc độ làm việc:

–

0 đến 8 MHz đối với Atmega8L.

–

0 đến 16 MHz đối với Atmega8.

– 22 – 22 4.4.2. Sơ đồ chân Atmega8

– 23 – 23 Hình 4.11 Sơ đồ chân Atmega8

4.4.3. Sơ đồ khối của Atmega8

– 24 – 24 Hình 4.12 Sơ đồ khối vi điều khiển AVR Atmega8

4.4.4. Mô tả chức năng các chân Atmega8

VCC: Điện áp nguồn nuôi.

GND: Đất.

Port B (PB0…PB7)

–

Port B là port I/O 8 bit với điện trở kéo lên ở bên trong, cung cấp dòng điện 40mA

có thể điều khiển trực tiếp led đơn.

–

Khi các chân Port B là các lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽ

là nguồn dòng nếu như các điện trở nối lên nguồn dương được kích hoạt. Các chân

này sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khi

không có dao động.

Port C (PC0…PC6)

–

Port C là port I/O 8 bit với điện trở kéo lên ở bên trong, cung cấp dòng điện 40mA

có thể điều khiển trực tiếp led đơn.

–

Khi các chân Port C là các lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽ

là nguồn dòng nếu như các điện trở nối lên nguồn dương được kích hoạt. Các chân

này sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khi

không có dao động.

–

Port C cũng đóng vai trò như 8 đường địa chỉ cao từ A8 đến A15 khi kết nối bộ

nhớ SRAM bên ngoài.

Port D (PD0…PD7)

–

Port D là port I/O 8 bit với điện trở kéo lên ở bên trong, cung cấp dòng điện 40mA

có thể điều khiển trực tiếp LED đơn.

–

Khi các chân Port D là các lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽ

là nguồn dòng nếu như các điện trở nối lên nguồn dương được kích hoạt. Các chân

– 25 – 25 này sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khi

không có dao động.

Reset: Ngõ vào được đặt lại. ATmega8 sẽ được đặt lại khi chân này ở mức thấp

trong hơn 50ns hoặc ngay cả khi không có tín hiệu xung clock. Các xung ngắn hơn

không tạo ra tín hiệu đặt lại.

AVCC: Cung cấp nguồn cho Port C và bộ chuyển đổi ADC hoạt động. Ngay khi

không sử dụng bộ chuyển đổi ADC thì chân AVCC vẫn phải đươc kết nối tới

nguồn VCC.

AREF: Đây là chân điều chỉnh điện áp tham chiếu cho chuyển đổi A/D.

XTAL1: Ngõ vào bộ khuếch đại đảo và ngõ vào mạch tạo xung nhịp bên ngoài.

XTAL2: Ngõ ra bộ khuếch đại đảo.

Bộ tạo dao động thạch anh :

–

XTAL1 và XTAL2 lần lượt là lối vào và lối ra của một bộ khuếch đại đảo, bộ

khuếch đại này được bố trí để làm bộ tạo dao động trên chip

–

Để điều khiển được bộ Vi Điều Khiển từ một nguồn xung nhịp bên ngoài, chân

XTAL2 để không, chân XTAL1 được nối với tín hiệu dao động bên ngoài.

– 2-25. Hoạt động với vận tốc đồng hồ đeo tay đến 20 MHz. So với những họ vi điều khiển khác thì viđiều khiển họ ATMEL có tần số xung nhịp được cho phép tương đối cao, đơn cử là từ 0 đến 20MH z tùy theo từng loại đơn cử. Xung nhịp do bộ xê dịch tạo ra cũng chínhlà xung nhịp của mạng lưới hệ thống, không hề phải qua bộ chia tần như trong trường hợp cácvi điều khiển sinh ra trước đó, nên kéo theo vận tốc giải quyết và xử lý lệnh cao. 6. Khả năng thực thi lệnh trong một chu kì xung nhịp, AVR có năng lực đạt đến tốcđộ giải quyết và xử lý 20 MPIS ( triệu lệnh trong một giây ) Hình 4.1 So sánh thời hạn thực thi lệnh giữa những bộ vi xử lýCác vi điều khiển SX cũng có tần số xung nhịp cao hơn ở những vi điều khiểnAVR nhưng lại có dòng tiêu thụ tương đối lớn, ngoài những lại không có những bộ phậnngoại vi trên chíp rất tiện lợi cho người dùng như vi điều khiển AVR. Chính cácbộ phận ngoại vi tích hợp đã góp thêm phần làm tăng vận tốc giải quyết và xử lý lệnh tính chung cho cảhệ thống. 7. Bộ nhớ chương trình và tài liệu được tích hợp ngay trên chíp AVR có tới 3 côngnghệ bộ nhớ khác nhau : Bộ nhớ EPROM xóa được kiểu Flash ( luôn luôn lập trình mới được ) dùng chomã chương trình mà người dùng hoàn toàn có thể lập trình được. – 3-3 Bộ nhớ EPROM hay PROM xóa được bằng điện, nhưng nội dung bộ nhớ vẫngiữ nguyên sau khi tắt điện áp nguồn. Chương trình người dùng hoàn toàn có thể được lậptrình trong thời hạn thựckhi mạng lưới hệ thống đang hoạt độngBộ nhớ RAM tĩnh ( SRAM ) dùng cho những biến, nội dung của bộ nhớ sẽ mất đikhi tắt điện áp nguồn. Ngoài ra, vi điều khiển AVR có tới 32 thanh ghi thao tác đanăng, tổng thể đều được nối trực tiếp với khối ALU ( đơn vị chức năng logic số học ) và được traođổi trực tiếp trên vùng địa chỉ bộ nhớ, đơn cử là 32 ô tiên phong của bộ nhớ ( 0x00 đến0xFF ) tương ứng với thanh ghi thao tác đa năng R0-R31. 8. Khả năng lập trình được trong mạng lưới hệ thống do cách phong cách thiết kế và công nghệ tiên tiến bộ nhớ đượcsử dụng mà những vi điều khiển hoàn toàn có thể được lập trình ngay khi đang còn cấp nguồntrên bản mạch. Không cần phải nhấc vi điều khiển ra ngoài bản mạch như nhiều họvi điều khiển khác. Các cổng tiếp xúc RS-232 và SPI cho phép thao tác dễ dàngthực hiện trên mạng lưới hệ thống. 9. Có vận tốc giải quyết và xử lý lớn hơn 12 lần so với những vi điều khiển CISC thường thì. 10. Hỗ trợ cho việc lập trình bằng ngôn từ bậc cao, ví dụ điển hình như ngôn từ C. 11. Tất cả những vi điều khiển đang lưu hành trên thị trường đều được sản xuất bằng côngnghệ CMOS 0.6 μm. 12. Điện áp thao tác được cho phép từ 2.7 V đến 6V. 13. Một kiến trúc đơn thuần và hài hòa và hợp lý sẽ giúp người dùng tìm hiểu và khám phá thuận tiện trong thờigian ngắn. 14. Tập lệnh AVR có tới 113 lệnh được cho phép lập trình một cách thuận tiện và đơn giảnbằng hợp ngữ, nhưng cấu trúc của bộ giải quyết và xử lý Atmel còn được cho phép lập trình bằngngôn ngữ C. 4.2. Cấu trúc phần cứng của họ vi điều khiển AVR4. 2.1. Tổng quan về kiến trúcCác thanh ghi đa năng truy vấn nhanh gồm 32 thanh ghi 8 bit được truy cậptrong một chu kì xung nhịp. Điều này có nghĩa là trong 1 chu kì xung nhịp ALU-4-4thực hiện được một phép toán : hai toán hạng được xuất từ những thanh ghi đa năng, phép toán được thực thi và hiệu quả được lưu trở lại vào tập những thanh ghi. 6 trongsố 32 thanh ghi này hoàn toàn có thể dùng làm con trỏ địa chỉ gián tiếp 16 bit để định địa chỉkhông gian tài liệu và cho phép tính địa chỉ hiệu dụng. Một trong 3 con trỏ địa chỉcũng được dùng làm con trỏ địa chỉ cho tính năng tìm kiếm bảng hằng số. Cácthanh ghi có công dụng bổ xung này là những thanh ghi 16 bit X, Y, Z.ALU : Hỗ trợ những công dụng số học và tính năng logic giữa những thanh ghi. Cácphép toán trong thanh ghi cũng được thực thi trong ALU.Hình 4.2 Kiến trúc của bộ giải quyết và xử lý AVRNgoài chính sách định địa chỉ gián tiếp thanh ghi, chính sách định địa chỉ bộ nhớthông thường cũng hoàn toàn có thể được dùng trong tập những thanh ghi đa năng. Nguyên nhânlà những thanh ghi đa năng được gán 32 địa chỉ thấp nhất trong khoảng trống tài liệu từ-5-5 $ 00 đếm $ 1F nên chúng được truy vấn những vị trí thường thì. Không gian bộ nhớ vào ra chứa 64 bit địa chỉ cho những tính năng ngoại vi củaCPU như những thanh ghi điều khiển, bộ Timer / Counter, bộ ADC và tính năng I / Okhác. Bộ nhớ I / O hoàn toàn có thể truy vấn trực tiếp hoặc như những vị trí trong khoảng trống dữliệu ngay sau những vị trí của tập những thanh ghi đa năng từ địa chỉ USD 20 đến USD 5F. AVR sử dụng kiến trúc Harvard với bộ nhớ và bus riêng không liên quan gì đến nhau cho chương trìnhvà tài liệu. Bộ nhớ chương trình được thực thi với một đường ống hai tầng. Trongkhi một lệnh đang được thực thi thì lệnh tiếp theo được nhập vào bộ nhớ chươngtrình. Giải pháp này được cho phép vác lệnh được thực thi trong mọi chu kì xung nhịp. Bộ nhớ chương trình là bộ nhớ Flash lập trình được. Trong quy trình gọi ngắt và chương trình con, địa chỉ quay trở lại của bộ đếm lệnhhay bộ đếm chương trình PC được đưa vào ngăn xếp. Ngăn xếp được cấp pháttrong bộ lưu dữ liệu SRAM nên kích cỡ chỉ bị số lượng giới hạn bởi dung tích vàkhông gian đã sử dụng của bộ nhớ SRAM. Tất cả chương trình của người dùngphải khởi tạo con trỏ ngăn xếp SP ( Stack Pointer ) khi mở màn chương trình ( trướckhi chương trình con và ngắt được thực thi ). Con trỏ ngăn xếp 16 bit SP được truycập để đọc / ghi trong khoảng trống vào / ra. Bộ nhớ SRAM hoàn toàn có thể được truy vấn dễdàng trải qua 5 chính sách định địa chỉ được phân phối trong kiến trúc AVR.Khối ngắt mềm dẻo có những thanh ghi điều khiển trong khoảng trống vào ra vàmột bit được cho phép ngắt toàn cục trong thanh ghi trạng thái. Mỗi ngắt đều có mộtvector ngắt riêng. Các ngắt có thứ tự ưu tiên tương ứng với thứ tự vector ngắt củachúng, địa chỉ của vector ngắt càng thấp thì thứ tự ưu tiên càng cao. 4.2.2. Các thanh ghi đa dụngTất cả những bộ vi điều khiển AVR đều có 32 thanh ghi đa năng. Một số trong cácthanh ghi này còn có những tính năng bổ xung. Tất cả thanh ghi được đặt tên từ R0đến R31, tệp thanh ghi được tách thành hai phần, mỗi phần có 16 thanh ghi đánh sốtừ R0 đến R15 và R16 đến R31. Tất cả những lệnh thao tác trên những thanh ghi đều có-6-6thể truy vấn trực tiếp và truy vấn trong quy trình đơn đến tổng thể những thanh ghi, nhưng có một ngoại lệ là những lệnh SBCI, SUBI, CPI, ANDI và ORI cũng như WI, những lệnh này chỉ tác động ảnh hưởng đến những thanh ghi từ R16 đến R31. Các thanh ghi R0 và R26 đến R31 có những công dụng bổ trợ. Thanh ghi R0được sử dụng trong những lệnh nạp bộ nhớ chương trình LPM ( Load ProgramMemory ), trong khi những thanh ghi R26 đến R31 được sử dụng làm những thanh ghicon trỏ như trong hình minh họa bên dưới. Các thanh ghi con trỏ này được sử dụngtrong nhiều lệnh gián tiếp trong thanh ghi. Hình 4.3 Tập thanh ghi của vi điều khiển AVR4. 2.3. Cổng ra vàoTất cả những vi điều khiển AVR đều có một lượng lớn những cổng vào ra nằm trongkhoảng 3 bit trên vi điều khiển loại 90S2313 đến 48 bit Mega103. Tất cả những cổngvào / ra của vi điều khiển AVR đều chịu được dòng điện đến 20 mA nên rất thích hợpvới việc điều khiển trực tiếp những led vì không cần đến những mạch đệm bổ trợ. Tất cả những cổng vào / ra đều có 3 địa chỉ vào / ra đi kèm với chúng, ba địa chỉ vàora đều cần được đặt thông số kỹ thuật cho những bít riêng không liên quan gì đến nhau thành lối vào hoặc thành lối ra, – 7-7 địa chỉ khác được cần đến để xuất dữ liệu và địa chỉ thứ 3 dùng để đọc tài liệu về ( lối vào ). Các cổng được đánh số DDRx, PORTx, PINx cho một cổng x cho trước. Để đọc tài liệu của phần lối vào của một cổng, ta sử dụng thanh ghi PINx. Thanh ghi PINx được tiếp nối đuôi nhau với chân của cổng. Chân của cổng hoàn toàn có thể cấp tínhiệu để duy trì trạng thái theo mức điện áp cao ( pull up ) bên trong bằng cách ghigiá trị “ 1 ” vào bit cổng ở vị trí PORTx. Các điện trở pull up có giá trị 30 kΩ đến150kΩ. Giá trị tương úng của dòng điện là 160 μA đến 33 μA. Hình 4.4 Các port đọc và ghiNgược lại nếu một giá trị “ 0 ” được ghi vào bit cổng ở địa chỉ PORTx thì trạngthái pull up và chân lối vào chuyển theo trạng thái trở kháng cao. 4.2.4. Bộ nhớ SRAMBộ nhớ SRAM có trong hầu hết những bộ vi giải quyết và xử lý của vi điều khiển AVR. Dunglượng của bộ nhớ SRAM đổi khác từ 128 byte tới 4 kbyte. Bộ nhớ SRAM được truynhập bằng cách sử dụng nhiều lệnh truy nhập tài liệu hoặc trực tiếp hoặc gián tiếp. – 8-8 Bộ nhớ SRAM cũng được sử dụng cho ngăn xếp, thời hạn truy nhập vào bộ nhớSRAM bằng 2 chu kì đồng hồ đeo tay. Giao tiếp với bộ nhớ SRAM ngoài. Trên những bộ vi điều khiển AVR cỡ lớn đều có năng lực liên kết với bộ nhớSRAM ở bên ngoài. Để được cho phép truy nhập bộ nhớ SRAM ngoài trên PortA vàPortC của những bộ điều khiển cũng như tín hiệu ALE dùng cho việc phân kênh địachỉ / tài liệu, bit SRE ( bit 7 ) trong thanh ghi MCUCR được đặt lên “ 1 ”. Thời giantruy nhập mặc định so với quy trình nhập lên SRAM ngoài là bằng 3 chu kì đồnghồ. Thời gian này hoàn toàn có thể làm tăng lên 4 chu kì đồng hồ đeo tay bằng cách thiết lập bit SRW ( bit6 ) trong thanh ghi MCUCR. Hình sau minh họa quy trình truy nhập mở rộngvới một trạng thái chờ bổ trợ thêm. Hình 4.5 Kết nối SRAM ngoài với bộ vi điều khiển4. 2.5. Cấu trúc ngắtNgắt là một cơ cấu tổ chức điều khiển dòng lệnh, cơ cấu tổ chức này được phong cách thiết kế trên hầu hếtcác bộ vi điều khiển. Trong quy trình tiếp xúc của mạng lưới hệ thống bộ vi giải quyết và xử lý với thế giớibên ngoài, nhiều vấn đề xảy ra theo cách không đồng điệu, điều này gây khó khăncho bộ giải quyết và xử lý khi mà phải kiểm tra tổng thể những thiết bị để giám sát sự chuyển dời củadữ liệu. Ngược lại, sẽ trở nên tốt hơn nếu những thiết bị này hoàn toàn có thể loan báo sự đến-9-9nơi của tài liệu. Đây là cả những gì mà cơ cấu tổ chức ngắt phải triển khai. Thiết bị ngoại visẽ ngắt việc thực thi chương trình chính và bộ giải quyết và xử lý tạm ngừng việc thực thichương trình thông thường để kiểm tra nguồn ngắt và triển khai những thao tác đápứng thiết yếu. Sau khi đã hoàn thành xong những thao tác thiết yếu, việc thực thi chươngtrình đã bị ngắt sẽ liên tục. Chương trình ngắt chỉ đơn thuần giống hệt như mộtchương trình con chỉ ngoại trừ một đặc thù là việc thực thi của đoạn chương trìnhngắt này không bị bộ giải quyết và xử lý chặn trước là sẽ Open vào thời gian đơn cử nào. Bộ vi điều khiện AVR có rất nhiều cấu trúc ngắt. Khả năng ngắt đã được chucấp cho hầu hết những thiết bị ngoại vi sao cho chương trình chính không cần phảithường xuyên kiểm tra những thiết bị này. 1. Thiết bị ngoại vi ngắt bộ xử lý2. Việc thực thi lệnh hiện tại được hoàn thành xong. 3. Địa chỉ của lệnh tiếp theo được tàng trữ trên ngăn xếp ( thuộc phần cứng hoặc phầnmềm ) 4. Địa chỉ ISR ( đoạn chương trình ngắt ) được nạp vào bộ đếm chương trình. 5. Bộ giải quyết và xử lý ISR. 6. Việc hoàn thành xong những thao tác thực thi ISR được chỉ báo bằng lệnh RETI. 7. Bộ giải quyết và xử lý nạp bộ đếm chương trình với giá trị được tàng trữ trên ngăn xếp và việcthực thi chương trình thông thường lại được liên tục. 4.2.6. Bộ so sánh analogBộ so sánh analog so sánh những giá trị điện áp lối vào, đơn cử là ở lối vào AINO ( AC + ) và AIN1 ( AC – ) với nhau. Nếu như điện áp ở lối vào AIN0 lớn hơn AIN1 thìlối ra của bộ so sánh analog ACO ( Analog Computer Output ) được đặt lên mức 1. Lối ra này hoàn toàn có thể cho bộ Timer / Counter 1 để trigger xóa ngắt bộ so sánh analog. – 10 – 10 – Hình 4.6 Sơ đồ khối của bộ so sánh AnalogBộ so sánh analog được điều khiển trải qua thanh ghi điều khiển và trạngthái so sánh analog, thường viết tắt là ACSR, tại địa chỉ $ 08 trong vùng địa chỉ I / Ohoặc địa chỉ nhớ USD 28 trong vùng địa chỉ nhớ tài liệu. Bảng 4.1 Sắp xếp những chân của bộ so sánh Analog4. 2.7. Bộ biến hóa A / D bên trongCác vi điều khiển AVR loại AT90S4434 / 8535 và Atmega 103 / 603 có một bộbiến đổi ADC với độ phân giải là 10 bit. Ngoài bộ ADC còn có bộ dồn kênh lối vào, mỗi lối hoàn toàn có thể được dẫn riêng không liên quan gì đến nhau tới bộhiển thị ADC. – 11 – 11 – Hình 4.7 Sơ đồ khối bộ biến hóa ADCBảng 4.2 Các thanh ghi điều khiển bộ biến hóa ADCThanh ghi điều khiển bộ dồn kênh ADC $ 07 ( USD 27 ) ADMUX – 12 – 12 Thanh ghi trạng thái điều khiển ADCADCSR $ 06 ( USD 26 ) Thanh ghi tài liệu ADC ( HIGH ) ADCH $ 05 ( USD 25 ) Thanh ghi tài liệu ADC ( LOW ) ADCL $ 04 ( USD 24 ) Bộ biến hóa ADC được biến hóa qua 4 thanh ghi ADMUX, ADCSR, ADCH vàADCR trong vùng địa chỉ vào ra. Bằng thanh ghi 3DMUX, một trong 8 kênh đượclựa chọn để đổi khác tín hiệu số. Bộ đổi khác hoàn toàn có thể hoạt động giải trí trong hai chính sách : Quá trình đổi khác được người dùng khởi độngQuá trình biến hóa diễn ra liên tụcBảng 4.3 Sự sắp xếp những chân lối vào của bộ biếm đổi ADCTín hiệuAT90S8535 / 4434ADC0 ADC1ADC2ADC3ADC4ADC5ADC6ADC7PA0PA1PA2PA3PA4PA5PA6PA7Việc kết thúc quy trình đổi khác nghĩa là thời gian mà một tín hiệu analog đãđược số hóa và chuẩn bị sẵn sàng chờ giải quyết và xử lý liên tục, sẽ được báo hiệu qua một cờ trongthanh ghi trạng thái ADC ( ADCSR ). Trong thanh ghi ADCSR này người dùng cóthể lựa chọn một trong hai chính sách. Kết quả của quy trình biến hóa A / D được đặt ởcác thanh ghi ADCH ( bit 8 và 9 ) và ADCL ( bit 0 đến 7 ). – 13 – 13 4.2.8. Bộ định thời watchdog bên trongBộ định thời Watchdog là bộ định thời điều khiển được và được sử dụng làmthiết bị thức tỉnh trong trường hợp phần mềm bị rơi vào một hoặc 1 số ít vòng lặpvô tận hoặc trong trường hợp việc thực thi chương trình bị mắc lỗi. Bộ định thờiwatchdog có một lối ra, có năng lực đặt lại bộ điều khiển. Hình bên dưới. Mạch định thời watchdog timer được giữ nhịp từ một bộ xê dịch RC riêngbiệt trên chip. Bằng cách điều khiển mạch chia tần số timer, khoảng chừng thời hạn resetmạch Watchdog hoàn toàn có thể kiểm soát và điều chỉnh như hình minh họa trong bảng sau những khoảngreset, mạch Watchdog cũng nhờ vào vào điện áp nguồn nuôi. Hình 4.8 Sơ đồ khối của bộ định thời Watchdog Chế độ hoạt động giải trí tiết kiệm ngân sách và chi phí nguồn năng lượng : Bộ vi giải quyết và xử lý AVR có nhiều năng lực làm giảm nguồn năng lượng tiêu thụ để chuyểnsang trạng thái ngủ ( sleep mode ), bit SE trong MCUCR ( mở thanh ghi điều khiểnbộ giải quyết và xử lý ) phải được đặt lên “ 1 ”, một lệnh sleep cần phải được thực thi. Nếu mộtngắt đã được được cho phép Open trong khi MCU đang ở trạng thái ngủ, thì MCU sẽthức dậy thực thi đoạn chương trình ( routine ) ngắt, và lại liên tục thực thi từ lệnhkế tiếp theo lệnh sleep. Nội dung của tập thanh ghi, SRAM, và bộ nhớ I / O vẫnđược giữ nguyên. Nếu một tín hiệu reset Open trong trạng thái ngủ thì MCU sẽthức dậy và thực thi từ vector reset. – 14 – 14 Khi SM bị xóa về không thì lệnh sleep bắt buộc MCU chuyển sang chế độnghỉ, làm ngưng hoạt động giải trí của CPU nhưng được cho phép bộ Timer / Counter Watchdogvà ngắt mạng lưới hệ thống liên tục hoạt động giải trí. Đặc tính này được cho phép MCU thức tỉnh và ngắtđược trigger từ bên ngoài cũng như ngắt bên trong giống như ngắt tràn bộ định thờivà đặt lại Watchdog. Nếu như sự thức tỉnh từ ngắt bộ so sánh analog không đượcyêu cầu, thì bộ so sánh analog hoàn toàn có thể bị ngắt nguồn nuôi bằng cách đặt bit ACDvào thanh ghi điều khiển và trạng thái analog ACSR. Biện pháp này làm giảm dòngtiêu thụ trong chính sách nghỉ. Khi MCU bị thức tỉnh khỏi chính sách nghỉ, đơn vị chức năng CPU khởi động chương trìnhchấp hành ngay lập tức. Khi bit SM được đặt lên “ 1 ”, lệnh sleep bắt buộc MCU chuyển sang chính sách tiếtkiệm nguồn năng lượng hay giảm dòng tiêu thụ. Trong chính sách này bộ giao động ngoài bịngưng hoạt động giải trí, trong khi những ngắt ngoài và Watchdog ( nếu đang ở trạng thái chophép ) hoạt động giải trí. Chỉ thao tác đặt lại ( reset ) bên ngoài. Thao tác đặt lại Watchdog ( nếu đang ở trạng thái được cho phép hoạt động giải trí ) hoặcngắt theo mức ngoài lên INT0 hoặc INT1 mới hoàn toàn có thể thức tỉnh MCU. Chú ý rằngmột khi ngắt trigger theo nức được sử dụng cho việc thức tỉnh khỏi trạng thái tiếtkiệm nguồn năng lượng thì mức thấp hơn cần nguồn năng lượng giữ trong khoảng chừng thời hạn dàihơn thời hạn làm trễ dài nhất ( Time out ) so với thao tác reset TOUT. Nếu khôngthì thiết bị sẽ không thức dậy. 4.3. Giới thiệu họ vi điều khiển Atmega 164.3.1. Đặc điểmAtmega16 là bộ vi điều khiển RISC 8 bit tiêu thụ ít nguồn năng lượng dựa trên kiếntrúc RISC AVR. Bằng việc triển khai những lệnh mạnh trong một chu kì xung nhịp, Atmega16 đạt đên vận tốc giải quyết và xử lý lệnh lên đến 1 triệu lệnh / giây ở tần số 1MH z. Viđiều khiển này còn được cho phép người phong cách thiết kế mạng lưới hệ thống tối ưu hóa mức độ tiêu thụnăng lượng mà vẫn bảo vệ vận tốc giải quyết và xử lý. – 15 – 15 Phần cốt lỏi của AVR tích hợp tập lệnh đa dạng chủng loại về số lượng với 32 thanh ghilàm việc đa năng. Toàn bộ 32 thanh ghi đều được nối với ALU cho truy vấn haithanh ghi độc lập bằng một lệnh đơn trong một chu kì xung nhịp. Kiến trúc đạt tốcđộ xủ lý nhanh gấp 10 lần so với vi điều khiển CISC ( Complex Instruction SetComputer ) thường thì. Atmega16 với kiến trúc RISC có chỉ tiêu chất lượng cao và tiêu thụ nguồn năng lượng ít : 131 lệnh hầu hết được triển khai trong một chu kỳ luân hồi xung nhịp. 32×8 thanh ghi thao tác đa năng. Tốc độ giải quyết và xử lý lệnh lên đến 16 triệu lệnh / giây ở tần số 16MH z. Bộ nhớ tài liệu và bộ nhớ chương trình không tự mất tài liệu : 16K byte bộ nhớ Flash lập trình được ngay trên mạng lưới hệ thống, hoàn toàn có thể ghi xóa 10000 lần. 512 byte bộ nhớ EEFROM lập trình được ngay trên mạng lưới hệ thống, hoàn toàn có thể ghi xóa100000 lần. 1K byte bộ nhớ SRAM. Khóa bảo mật thông tin ứng dụng lập trình được. Giao diện tiếp nối đuôi nhau SPI để lập trình ngay trên mạng lưới hệ thống. Các tính năng ngoại vi : Hai bộ đếm / bộ định thời 8 bit với chính sách so sánh và chia tần số tách biệt. Một bộ định thời 16 bit với chính sách so sánh, chia tần số tách biệt và chính sách bắt mẫu ( Capture Mode ). Bộ đếm thời hạn thực ( RTC ) với bộ xê dịch tách biệt. Bốn kênh PWM điều chế độ rộng xung. Bộ biến hóa ADC bên trong 8 kênh 10 bit. Bộ USART tiếp nối đuôi nhau lập trình được. Bộ định thời Watchdog lập trình được với bộ giao động trên chip. Bộ so sánh Analog ngay trên chip. Các tính năng vi điều khiển đặc biệt quan trọng : Có mạch power – on reset và hoàn toàn có thể reset bằng ứng dụng. – 16 – 16 Các nguồn ngắt ngoài và trong. Có 6 chính sách ngủ : nghỉ ( Idle ). Tiết kiệm nguồn năng lượng ( power save ) và power down, ADC Noise Reduction, Standby and Extended Standby. Tần số thao tác hoàn toàn có thể đổi khác được bằng ứng dụng. Vào ra và những cách đóng vỏ 32 đường vào ra lập trình được. 44 chân dán kiểu vỏ vuông ( TQFP ) Điện thế thao tác : VCC = 2,7 V đến 5,5 V so với Atmega16L. VCC = 4,5 V đến 5,5 V so với Atmega16. Vùng vận tốc thao tác : 0 đến 8 MHz so với Atmega16L. 0 đến 16 MHz so với Atmega16. 4.3.2. Sơ đồ chân Atmega16Hình 4.9 Sơ đồ chân Atmega16 – 17 – 17 – 4.3.3. Sơ đồ khối của Atmega16 – 18 – 18 Hình 4.10 Sơ đồ khối vi điều khiển AVR Atmega164. 3.4. Mô tả tính năng những chân Atmega16 Vcc : điện áp nguồn nuôi GND : nối đất PORT A ( PA0 … PA7 ) : có nhiều công dụng : Là ngõ vào tín hiệu để quy đổi A / DLà cổng vào ra 8 bit nếu như biến hóa A / D không sử dụng, những chân củaPort A có những điện trở nối lên nguồn dương. Port A hoàn toàn có thể phân phối nguồnđiện 20 mA và điều khiển trực tiếp led hiển thị. Khi những chân Port A là những lối vào được đặt xuống mức thấp ở bên ngoài chúng sẽlà nguồn dòng nếu như những điện trở nối lên nguồn dương được kích hoạt. Các chânnày sẽ ở trạng thái tổng trở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khikhông có tín hiệu giữ nhịp. PORT B ( PB0 … PB7 ) Là cổng vào ra 8 bit, có điện trở kéo lên ở bên trong, hoàn toàn có thể cung ứng dòng điện20mA. Khi port B là port nhập vào ( in put ) và những ngõ ra ở mức thấp ( low ) thì portB đóng vai trò là nguồn dòng nếu những điện trở kéo lên được kích hoạt. Port B sẽ ởtrạng thái tổng trở cao khi vi điều khiển bị reset hoặc khi không có giao động. PORT C ( PC0 … PC7 ) Là cổng vào ra theo hai hướng 8 bit. Các chân của Port C có những điện trở nối lênnguồn dương. Ngõ ra port C hoàn toàn có thể cho dòng 20 mA đi qua và điều khiển trực tiếpled hiển thị. Khi những chân port C là những lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽlà nguồn dòng nếu những điện trở nối lên nguồn dương được kích hoạt. những chân nàysẽ ở trạng thái tổng trở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khikhông có tín hiệu giữ nhịp. PORT D ( PD0 … PD7 ) – 19 – 19 – Là cổng vào ra theo hai hướng 8 bit. Các chân của Port D có những điện trở nối lênnguồn dương. Ngõ ra port D hoàn toàn có thể cho dòng 20 mA đi qua và điều khiển trực tiếpled hiển thị. Khi những chân port D là những lối vào được đặt xuống mức thấp từ bênngoài, chúng sẽ là nguồn dòng nếu những điệntrở nối lên nguồn dương được kích hoạt. những chân này sẽ ở trạng thái tổngtrở cao khi tín hiệu reset ở mức tích cực hoặc ngay cả khi không có tínhiệu giữ nhịp. Cung cấp những tính năng tương ứng với những công dụng đặc biệt quan trọng. Reset : là lối vào đặt lại. Bộ vi điều khiển sẽ được đặt lại khi chân này ở mức thấptrong hơn 50 ns ngay cả khi có tín hiệu giữ nhịp. Các xung ngắn hơn không tạo ratín hiệu đặt lại. XTAL1 : Lối vào mạch khuếch đại hòn đảo và lối vào mạch tạo xung nhịp bên trong. XTAL2 : Lối vào bộ khuếch đại ảo. ICP : Chân vào có tính năng bắt tín hiệu cho Timer / Cuonter 1 ALE : Là chân tín hiệu được cho phép chốt địa chỉ ( adress latch enable ) được dùng khitruy nhập bộ nhớ ngoài. Xung ALE được dùng để chốt bit địa chỉ trong chu kì truycập bộ nhó thứ nhất. Sau đó những chân AD0 … AD7 được dùng làm những đường dữliệu trong chu kì truy nhập bộ nhớ thứ hai ( AT90S8515 ). Bộ tạo xê dịch thạch anh : XTAL1 và XTAL2 lần lượt là lối vào và lối ra của mộtbộ khuếch đại hòn đảo, bộ khuếch đại này được sắp xếp để làm bộ tạo xê dịch trên chipnhư hình 4.3. Một bộ cộng hưởng tinh thể thạch anh hoặc một bộ cộng hưởng gốmcó thể sử dụng. Để điều khiển vi điều khiển bằng nguồn xung nhịp bên ngoài thìchân XTAL2 để không và nối XTAL một với tín hiệu giao động bên ngoài. 4.4. Giới thiệu vi điều khiển Atmega84. 4.1. Đặc điểmVi điều khiển Atmega8 của hãng ATMEL là một loại vi điều khiển AVR mớivới kiến trúc rất phức tạp. – 20 – 20 Atmega 8 là bộ vi điều khiển RISC 8 bit tiêu thụ nguồn năng lượng nhưng đạt hiệusuất rất cao, dựa trên kiến trúc RISC AVR. Bằng việc triển khai những lệnh trong mộtchu kỳ xung nhịp, Atmega8 đạt được vận tốc giải quyết và xử lý tài liệu lên đến 1 triệu lệnh / giâyở tần số 1MH z. Atmega8 còn được cho phép người phong cách thiết kế mạng lưới hệ thống tối ưu hóa mức độtiêu thụ nguồn năng lượng mà vẫn bảo vệ vận tốc giải quyết và xử lý. Atmega 8 đã tích hợp rất đầy đủ những tính năng như bộ chuyển đổi ADC 10 bit, bộso sánh, bộ truyền nhận tiếp nối đuôi nhau, bộ định thời, bộ đếm thời hạn thực, bộ điều chếđộ rộng xung … Do đó ta phải điều tra và nghiên cứu và khai thác triệt để những tính năng này đểứng dụng hiệu suất cao vào những mạch trong trong thực tiễn. Atmega8 sử dụng kiến trúc RISC ( Reduced Instruction Set Computer ) AVR. Atmega8 với kiến trúc RISC có chỉ tiêu chất lượng cao và tiêu thụ nguồn năng lượng ít : 130 lệnh hầu hết được triển khai trong một chu kỳ luân hồi xung nhịp. 32 thanh ghi thao tác đa năng. Tốc độ giải quyết và xử lý lệnh lên đến 16 triệu lệnh / giây ở tần số 16MH z. Bộ nhớ tài liệu và bộ nhớ chương trình không tự mất tài liệu : 8K byte bộ nhớ Flash lập trình được ngay trên mạng lưới hệ thống, hoàn toàn có thể nạp xóa 10000 lần. 512 byte bộ nhớ EEFROM lập trình được ngay trên mạng lưới hệ thống, hoàn toàn có thể ghi xóa100000 lần. 1K byte bộ nhớ SRAM.Có thể tiếp xúc với 8K byte bộ nhớ ngoài. Khóa bảo mật thông tin ứng dụng lập trình được. Giao diện tiếp nối đuôi nhau SPI để lập trình ngay trên mạng lưới hệ thống. Các tính năng ngoại vi : Hai bộ đếm / bộ định thời 8 bit với chính sách so sánh và chia tần số tách biệt. Một bộ định thời 16 bit với chính sách so sánh, chia tần số tách biệt và chính sách bắt mẫu ( Capture Mode ). Bộ đếm thời hạn thực ( RTC ) với bộ giao động tách biệt. Bộ điều chế độ rộng xung PWM 8 bit. – 21 – 21 – Bộ biến hóa ADC bên trong 8 kênh 10 bit. 2 bộ USART tiếp nối đuôi nhau lập trình được. Bộ định thời Watchdog lập trình được với bộ xê dịch trên chip. Một bộ so sánh Analog. Các tính năng vi điều khiển đặc biệt quan trọng : Có mạch power – on reset và hoàn toàn có thể reset bằng ứng dụng. Các nguồn ngắt ngoài và trong. Có 5 chính sách ngủ : nghỉ ( Idle ). Tiết kiệm nguồn năng lượng ( power save ) và power down, ADC Noise Reduction, Standby. Tần số thao tác hoàn toàn có thể đổi khác được bằng ứng dụng. Vào ra và những cách đóng vỏ23 đường vào ra lập trình được. 32 chân dán kiểu vỏ vuông ( TQFP ) Điện thế thao tác : VCC = 2,7 V đến 5,5 V so với Atmega8L. VCC = 4,5 V đến 5,5 V so với Atmega8. Vùng vận tốc thao tác : 0 đến 8 MHz so với Atmega8L. 0 đến 16 MHz so với Atmega8. – 22 – 22 4.4.2. Sơ đồ chân Atmega8 – 23 – 23 Hình 4.11 Sơ đồ chân Atmega84. 4.3. Sơ đồ khối của Atmega8 – 24 – 24 Hình 4.12 Sơ đồ khối vi điều khiển AVR Atmega84. 4.4. Mô tả công dụng những chân Atmega8 VCC : Điện áp nguồn nuôi. GND : Đất. Port B ( PB0 … PB7 ) Port B là port I / O 8 bit với điện trở kéo lên ở bên trong, phân phối dòng điện 40 mAcó thể điều khiển trực tiếp led đơn. Khi những chân Port B là những lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽlà nguồn dòng nếu như những điện trở nối lên nguồn dương được kích hoạt. Các chânnày sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khikhông có giao động. Port C ( PC0 … PC6 ) Port C là port I / O 8 bit với điện trở kéo lên ở bên trong, cung ứng dòng điện 40 mAcó thể điều khiển trực tiếp led đơn. Khi những chân Port C là những lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽlà nguồn dòng nếu như những điện trở nối lên nguồn dương được kích hoạt. Các chânnày sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khikhông có giao động. Port C cũng đóng vai trò như 8 đường địa chỉ cao từ A8 đến A15 khi liên kết bộnhớ SRAM bên ngoài. Port D ( PD0 … PD7 ) Port D là port I / O 8 bit với điện trở kéo lên ở bên trong, phân phối dòng điện 40 mAcó thể điều khiển trực tiếp LED đơn. Khi những chân Port D là những lối vào được đặt xuống mức thấp từ bên ngoài, chúng sẽlà nguồn dòng nếu như những điện trở nối lên nguồn dương được kích hoạt. Các chân – 25 – 25 này sẽ ở trạng thái tổng trở cao khi tín hiệu Reset ở mức tích cực hoặc ngay cả khikhông có xê dịch. Reset : Ngõ vào được đặt lại. ATmega8 sẽ được đặt lại khi chân này ở mức thấptrong hơn 50 ns hoặc ngay cả khi không có tín hiệu xung clock. Các xung ngắn hơnkhông tạo ra tín hiệu đặt lại. AVCC : Cung cấp nguồn cho Port C và bộ chuyển đổi ADC hoạt động giải trí. Ngay khikhông sử dụng bộ chuyển đổi ADC thì chân AVCC vẫn phải đươc liên kết tớinguồn VCC. AREF : Đây là chân kiểm soát và điều chỉnh điện áp tham chiếu cho quy đổi A / D. XTAL1 : Ngõ vào bộ khuếch đại hòn đảo và ngõ vào mạch tạo xung nhịp bên ngoài. XTAL2 : Ngõ ra bộ khuếch đại hòn đảo. Bộ tạo giao động thạch anh : XTAL1 và XTAL2 lần lượt là lối vào và lối ra của một bộ khuếch đại hòn đảo, bộkhuếch đại này được sắp xếp để làm bộ tạo giao động trên chipĐể điều khiển được bộ Vi Điều Khiển từ một nguồn xung nhịp bên ngoài, chânXTAL2 để không, chân XTAL1 được nối với tín hiệu xê dịch bên ngoài .

Source: https://vh2.com.vn

Category : Tin Học